# (12) United States Patent

Spencer et al.

US 8,017,412 B2 (10) Patent No.:

(45) Date of Patent: Sep. 13, 2011

## (54) BETAVOLTAIC BATTERY WITH A SHALLOW JUNCTION AND A METHOD FOR MAKING **SAME**

(75) Inventors: Michael Spencer, Ithaca, NY (US);

MVS Chandrashekhar, Columbia, SC

Assignee: Widetronix, Inc., Ithaca, NY (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

Appl. No.: 12/888,521

Filed: Sep. 23, 2010

#### (65)**Prior Publication Data**

US 2011/0086456 A1 Apr. 14, 2011

## Related U.S. Application Data

- (60) Provisional application No. 61/250,504, filed on Oct. 10, 2009.

- (51) Int. Cl. H01L 21/00 (2006.01)

- (52) **U.S. Cl.** ...... 438/19; 438/56; 257/E21.465

- 438/56, FOR. 251; 257/E21.465 See application file for complete search history.

#### (56)**References Cited**

#### U.S. PATENT DOCUMENTS

| 5,187,547    |      |         | Niina et al 257/77       |

|--------------|------|---------|--------------------------|

| 7,527,869    | B2 * | 5/2009  | Kaneko et al 428/446     |

| 7,637,998    | B2 * | 12/2009 | Kaneko et al 117/54      |

| 2003/0070611 | A1*  | 4/2003  | Nakamura et al 117/109   |

| 2004/0237879 | A1*  | 12/2004 | Kaneko et al 117/2       |

| 2007/0284565 | A1*  | 12/2007 | Leatherdale et al 257/13 |

| 2009/0038538 | A1*  | 2/2009  | Kaneko et al 117/54      |

<sup>\*</sup> cited by examiner

Primary Examiner — Jarrett Stark

(74) Attorney, Agent, or Firm — Maxvalueip, LLC

#### (57)ABSTRACT

This is a novel SiC betavoltaic device (as an example) which comprises one or more "ultra shallow" P+N- SiC junctions and a pillared or planar device surface (as an example). Junctions are deemed "ultra shallow", since the thin junction layer (which is proximal to the device's radioactive source) is only 300 nm to 5 nm thick (as an example). In one example, tritium is used as a fuel source. In other embodiments, radioisotopes (such as Nickel-63, promethium or phosphorus-33) may be used. Low energy beta sources, such as tritium, emit low energy beta-electrons that penetrate very shallow distances (as shallow as 5 nm) in semiconductors, including SiC, and can result in electron-hole pair creation near the surface of a semiconductor device rather than pair creation in a device's depletion region. By contrast, as a high energy electron penetrates a semiconductor device surface, such as a diode surface, it produces electron hole-pairs that can be collected at (by drift) and near (by diffusion) the depletion region of the device. This is a betavoltaic device, made of ultra-shallow junctions, which allows such penetration of emitted lower energy electrons, thus, reducing or eliminating losses through electron-hole pair recombination at the surface.

# 26 Claims, 5 Drawing Sheets

FIG 1

FIG 2

FIG 3

Fig. 4

Fig. 5

# BETAVOLTAIC BATTERY WITH A SHALLOW JUNCTION AND A METHOD FOR MAKING **SAME**

## RELATED APPLICATIONS

This current application is a continuation of (related to) a prior provisional application, Ser. No. 61/250,504, filed 10 Oct. 2009, with the same inventor(s), same assignee (Widetronix Corporation), and the same title.

### BACKGROUND OF THE INVENTION

There are several technical constraints that must be considered when designing a low cost, manufacturable, high 15 volume, high power density silicon carbide (SiC) betavoltaic device. First, consideration must be given to the energy profile of radioisotopes to be used, and the volume at which such material can be produced. For example, tritium is one of the several viable radioisotope candidates, since it can be pro- 20 duced in sufficient quantities to support high volume device manufacture, and its energy profile fits well with a range of power generation design parameters.

Secondly, in order to produce high power density in betavoltaics, a large device surface area is required. There are 25 issued and pending betavoltaic patents that mention patterning methods for pillars, pores or other structures which yield such high surface area—patent application Ser. No. 11/509, 323 is an example, and can be used as a reference for pillared betavoltaic device construction. These methods must be opti- 30 mized appropriately in order to meet fabrication objectives, while controlling costs.

Thirdly, SiC has been shown to be the ideal material for betavoltaic devices, e.g. see reference patent application Ser. cation and design requirements which must be met in order to produce a workable device. For example, fabrication of SiC devices requires high temperature epitaxial processes. Because of such high temperature requirements, these epitaxial processes add an element of complexity and cost, not 40 seen with processes relating to other semiconductors, such as Si, and must be taken into account accordingly, or fabrication techniques must be developed to remove such complex and costly processes entirely.

Fourthly, it is desirable to integrate betavoltaic devices 45 directly with Silicon (Si)-based electronics, including, but not limited to, microprocessor and memory devices. Thus, there is a need for designs and fabrication processes which anticipate such integration.

A device which addresses or anticipates the aforemen- 50 tioned design considerations is disclosed herein. Methods for fabricating same are also disclosed.

### SUMMARY OF THE INVENTION

This invention is a novel SiC betavoltaic device which comprises one or more "ultra shallow" P+N<sup>-</sup> SiC junctions and a pillared or planar device surface. Junctions are deemed "ultra shallow", since the thin junction layer (which is proximal to the device's radioactive source) is only 300 nm to 5 nm 60

In one embodiment of this invention, tritium is used as a fuel source. In other embodiments, radioisotopes (such as Nickel-63, promethium or phosphorus-33) may be used. For the remainder of this disclosure, and for purposes of illustra- 65 tion/example, tritium will be referenced as an exemplary fuel source. It should also be noted that, although SiC is described

2

herein as the preferred semiconductor for this invention, other semiconductors, such as diamond and Group III-V nitrides, may also be used. For the remainder of this disclosure, and for purposes of illustration only, SiC will be referenced as an exemplary semiconductor. However, other similar semiconductors, dopants, and radioisotopes are also meant to be cov-

Low energy beta sources, such as tritium, emit low energy beta-electrons that penetrate very shallow distances (as shallow as 5 nm) in semiconductors, including SiC, and can result in electron-hole pair creation near the surface of a semiconductor device rather than pair creation in a device's depletion region. By contrast, as a high energy electron penetrates a semiconductor device surface, such as a diode surface, it produces electron hole-pairs that can be collected at (by drift) and near (by diffusion) the depletion region of the device. If electron-hole pairs created by low energy beta-electrons are generated near the surface of a device, they will recombine there, due to interaction with surface states (i.e. defects occurring at the termination site of crystals and serving as sites for minority carrier loss), and will not be available for power generation.

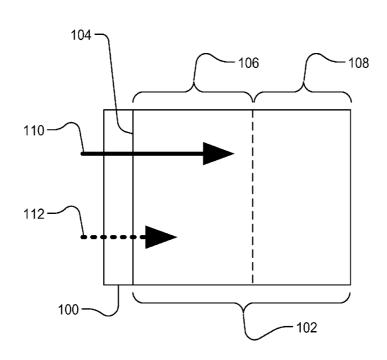

Thus, with knowledge of a lower energy beta-electron's path length, it is desirable to create thin, or ultra-shallow, junctions, which enable even the lowest energy electrons to penetrate well into the depletion region. This invention is a betavoltaic device comprising ultra-shallow junctions which allow such penetration of emitted lower energy electrons, thus, reducing or eliminating losses through electron-hole pair recombination at the surface (see FIG. 1).

# BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 shows the shallow P+N homojunction (interface at No. 11/509,323. However, SiC has unique processing, fabri- 35 104). Dashed arrow (112) indicates lower energy electrons penetrating into the device, while solid arrow (110) indicates higher energy electron penetration. Area 100 indicates P layer, while area 102 indicates N layer, with depletion layer separated at 106 region (versus 108 region).

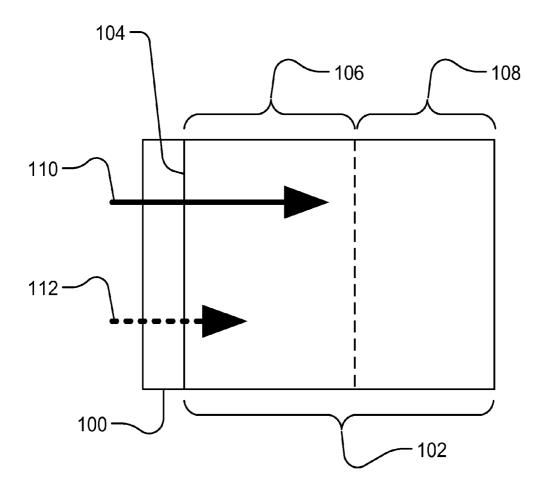

> FIG. 2 shows the implementation of liquid-based (212) doping for thin P+ region, on substrate 216, in container or chamber 210, using a holder 214.

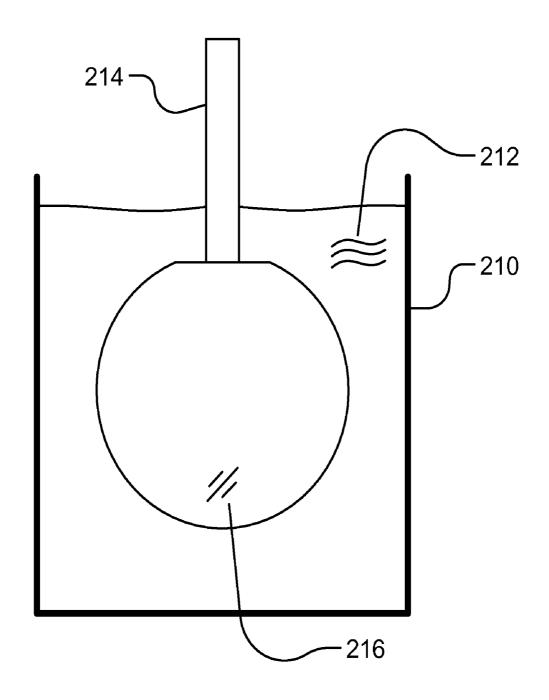

> FIG. 3 shows betavoltaic device implemented using both sides of a full substrate (300). One or more V-Grooves (302, 304, and 306) are on each side of the substrate (300), with a thin p-layer (310 and 312). Areas (narrow lines) 310 and 312 indicate P-layer, and area 308 indicates N-layer.

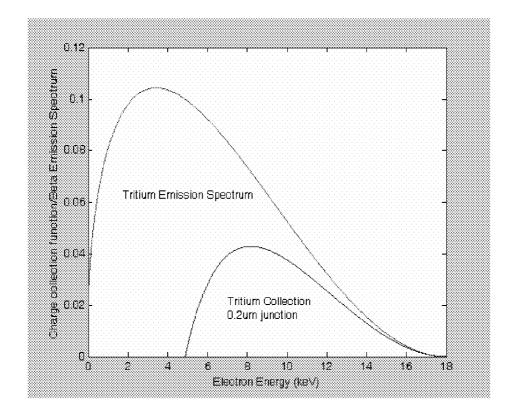

> FIG. 4 shows the charge collection function/beta emission spectrum, versus electron energy (KeV), for Tritium emission spectrum (the upper curve) and Tritium collection (0.2 micron) junction (the lower curve).

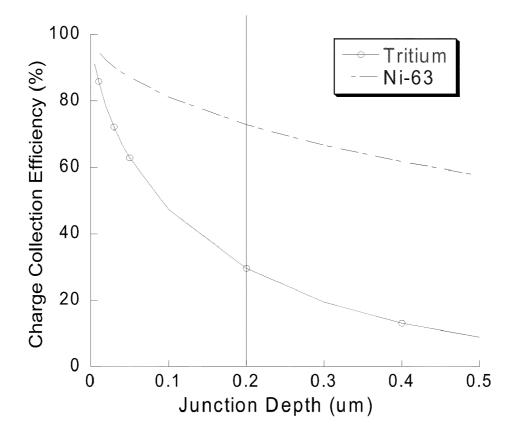

FIG. 5 shows the charge collection efficiency (in percentage) versus junction depth (in micron), for Tritium (denoted as the solid line with small circles) and for Ni-63 (denoted as 55 the dashed line, with a higher efficiency, at a given depth).

# DETAILED EMBODIMENTS OF THE INVENTION

Maximizing Charge Collection in SiC Betavoltaics

# Influence of Junction Depth

To quantify the extent of the surface, it is necessary to know the penetration depth, or range,  $R_B$  in  $\mu$ m, of the beta electron in the semiconductor, which is given as:

$$R_B(\mu \text{m}) = [4 \times E_0^{1.75} (\text{keV})/100]/\rho (\text{g/cm}^3)$$

3

where  $E_0$  is the incident beta energy in keV, and  $\rho$  is the density of the semiconductor in g/cm<sup>3</sup>. The penetration depth is simply a function of the energy spectrum of the  $\beta$ -radiation, which is known. The spectrum, to first order, is given by

$$f(E_0) = K \sqrt{E_0^2 + 2mc^2 E_0 (E_0(\text{max}) - E_0)^2}$$

(2)

where f(E) is the energy distribution function, m the electronic mass, c the speed of light, and K a normalization constant, such that we have:

$$\int_{a}^{E_0(max)} f(E_0) dE_0 = 1$$

(3)

The energy extends to a maximum,  $E_0(\max)$ , that typically lies at ~3 times the mean energy. For a given beta emitting isotope, a single  $E_0(\max)$  completely specifies the spectrum, as eq. 2 indicates. There is a Coulombic penetration factor that modifies equation (2) above. This factor accounts for 20 electrons being retarded by the Coulombic attraction from the nucleus, which skews the spectrum towards lower energies. Considering this factor, equation (2) becomes:

$$f(E_0) = KF(Z_D, E_0) \sqrt{E_0^2 + 2mc^2 E} (E_0(\text{max}) - E_0)^2$$

(4)

where  $F(Z_D, E_0)$ , called the Fermi function, takes into account the Coulombic penetration effects. This function is tabulated in relevant semiconductor literature, and is related to the daughter nucleus atomic number,  $Z_D$ , and the energy of the emitted  $\beta$  particle,  $E_0$ . It can be approximated by:

$$F(Z_D, E_0) = \frac{2\pi v}{1 - \exp(-2\pi v)}$$

(5)

where

$$v = 1.16 \times 10^{-3} Z_D \left/ \sqrt{\frac{E_0^2 + 2mc^2 E_0}{m^2 c^4 + E_0^2 + 2mc^2 E_0}} \right.$$

The penetration depth is then estimated as described in equation (1). From (4), ~65% of the spectrum energy lies at or below the mean, 5.5 keV for Tritium, while >80% of the energy lies below E(max)/2, which is ~9 keV for Tritium.

Assuming that all the beta-generated electron-holes 45 beyond the surface junction p-type layer are collected, while none of those generated in the surface junction layer are collected, we can estimate the charge collection as a function of energy, or as simply the fraction of the total path length  $(R_B)$  that lies beyond the junction region  $(X_j)$ . This fraction at 50 each energy in the beta spectrum is  $(R_B - X_j)/R_B$ .

Integrating the total charge collection function, we obtain the total charge collection efficiency. FIG. 4 illustrates the charge collection function of tritium, for a given junction depth of 0.2 µm. For reference, the incident beta spectrum is 55 shown. Finally, FIG. 5 shows the total charge collection efficiency as a function of junction depth. It is clear that, for tritium, the cheapest and most practical isotope for higher powered cells, junctions <50 nm must be fabricated, to achieve higher charge collection efficiencies.

When ultra-shallow P+N<sup>-</sup> junctions are utilized, the junction layer which is proximal to the device's radioactive source (the p-type surface junction layer mentioned above) is thin enough to permit source particle penetration deeper into the second junction layer (n-type layer) of the device. However, 65 the p-type layer is also sufficiently thick to allow electronhole pairs produced in the device to be collected/retained by

4

internal electric fields of the junction, rather than being lost due to surface state interactions.

The limitation on the thickness of a thin P+ layer depends on the doping concentration of that layer. The thickness of the P+ layer must be sufficient to contain the internal electric fields of the P+N<sup>-</sup> junction at zero bias and forward bias (under high energy electron irradiation). Another consequence of this requirement is that the surface depletion should be less than the junction depth, so that there is adequate conduction to make a contact to the p+ top region. The surface depletion is given as:

$$X_{d,surface} = \operatorname{sqrt}(((2^* \epsilon_{SiC})^* (V_{surface}))/(q^* N_A))$$

(6),

15 assuming that the surface barrier,  $V_{surface}$  is 1V, typical for SiC.  $\epsilon_{SiC}$  is the dielectric constant of SiC, q is the electronic charge, while  $N_A$  is the free hole concentration in the p+ SiC junction cap layer. This equation predicts that the P+ layer must be at least 300 nm, if a doping of  $10^{18}$  cm<sup>-3</sup> is used, and can be reduced to 30 nm, if a doping in the P+ region of  $10^{20}$  cm<sup>-3</sup> realized. Thus, if a doping of  $10^{18}$  cm<sup>-3</sup> is used, the junction depth must be 0.3  $\mu$ m or greater, which means that the charge collection efficiency will be less than 25%.

Based on the requirements for a tritium betavoltaic cell junction depth, described above, ultra-shallow junctions (below 30 nm), resulting from doping >10<sup>20</sup> cm<sup>-3</sup>, must be realized, to achieve greater than 60% charge collection efficiency. Further reduction of the junction, due to higher doping densities, will allow charge collection efficiencies to approach 90%. With a sufficiently doped, thin p-layer, even lower energy electrons from a lower energy radioactive source can penetrate the device, so as to avoid surface recombination or interaction with surface states, and produce electron-hole pairs that are collected by internal junction fields (and are not lost).

In one embodiment of this invention, a maximum depth of particle absorption is  $2 \, \mu m$ , and a doping level of  $10^{14} \, cm^{-3}$  is used for a thicker N-region, and a thin p+ region is formed (and doped at very high levels in accordance with the above discussions and formulations). In this embodiment, beta electrons from a tritium source will be captured in the internal fields of the junction formed by the N-region and the thin P+ region.

Doping described above, at levels >10<sup>20</sup> cm<sup>-3</sup>, makes doping more complex, since the amount of p-dopants needed in SiC (aluminum and boron are examples of dopants) is substantial, requiring highly degenerate doping. Furthermore, typical commercial techniques used to fabricate SiC junctions, such as chemical vapor deposition (CVD) and ionimplantation, cannot easily and cost effectively meet the extreme/tight junction depth and doping tolerances for ultrashallow junctions. Thus, new and effective methods must be created

A highly-doped, thin P+ region may be formed, using a liquid based process (see FIG. 2). In one embodiment of this process a SiC wafer is dipped into a 400 degrees C. to 1200 degrees C. liquid, comprising Si, C, and Al. Upon removal of the wafer an extremely thin P+ layer of SiC with a thickness of 5 nm to 300 nm, and doped with Al at carrier concentrations of 10<sup>18</sup> cm<sup>-3</sup> to greater than 10<sup>20</sup> cm<sup>-3</sup>, is formed.

In one embodiment of this invention, the concentrations of Si, C and Al are 94.5%, 0.5% and 5%, respectively. In alternative embodiments of this process, other concentrations of Si, C and Al may be used, with each element being no greater than 95%, 3% and 30%, respectively. In further embodiments, Ge may be added with Si, C and Al, with a concentration of no greater than 95%. This also applies to similar

20

5

materials or methods, for any other dopants or semiconductors, such as group IV or compound III-V.

In another embodiment, such concentrations of Si, C and Al may be evaporated on the surface of the SiC. In further embodiments of this evaporation process, Si may be replaced 5 with Ge, at concentrations referenced above for Si. The structure is heated to between 400 degrees C. and 1200 degrees C.. and a thin layer of liquid forms on the SiC surface. This layer first dissolves a small amount of SiC, and then after cooling, the SiC is recrystallized with a significant amount of Al doping. Doping performed in this manner is conformal, and can be used for planar SiC or SiC with pillars.

This also applies to similar heating methods, such as pulsed, uniform, localized, ramping up and down, uniform 15 ramping up, multiple exposures or single session, or operating at a lower temperature but at longer periods, to achieve the same effect on the doping and distribution of the dopants, or higher activation efficiencies for the dopants, or with sharper edges or doping profiles.

The doping methods described herein enable the manufacture of pillared or planar betavoltaic devices in a low cost batch process, which does not require high temperature SiC epitaxial processes such as chemical vapor deposition. Since high temperature gas phase epitaxial processes are elimi- 25 nated, direct manufacture of betavoltaic devices from substrates is now possible, and fabrication processes, including Si-based processes, requiring temperatures lower than those relating to SiC epitaxy, can be utilized, all of which results in substantial manufacturing cost savings.

FIG. 3 shows betavoltaic structures that can be fabricated, when the constraints of high temperature epitaxy are removed. Due to its lower temperature requirements, this technology can be directly integrated with Si-based processes, such as "Smartcut" processes, which enable betavoltaic device integration with Si-based electronics. Other Sibased processes may also be used with the methods described

More details are described here in the following figures: 40 FIG. 1 shows the shallow P+N homojunction (interface at 104). Dashed arrow (112) indicates lower energy electrons penetrating into the device, while solid arrow (110) indicates higher energy electron penetration. Area 100 indicates P layer, while area 102 indicates N layer, with depletion layer 45 separated at 106 region (versus 108 region).

FIG. 2 shows the implementation of liquid-based (212) doping for thin P+ region, on substrate 216, in container or chamber 210, using a holder 214.

FIG. 3 shows betavoltaic device implemented using both 50 sides of a full substrate (300). One or more V-Grooves (302, 304, and 306) are on each side of the substrate (300), with a thin p-layer (310 and 312). Areas (narrow lines) 310 and 312 indicate P-layer, and area 308 indicates N-layer.

FIG. 4 shows the charge collection function/beta emission 55 spectrum, versus electron energy (KeV), for Tritium emission spectrum (the upper curve) and Tritium collection (0.2 micron) junction (the lower curve).

FIG. 5 shows the charge collection efficiency (in percentage) versus junction depth (in micron), for Tritium (denoted 60 as the solid line with small circles) and for Ni-63 (denoted as the dashed line, with a higher efficiency, at a given depth).

In one embodiment of this invention, the growth rate of a P-doped layer can be calibrated for a few growth samples, such that the thickness of the Pregion is measured, e.g. by CV 65 or SIMS measurements, to find the junction between P and N types, and to calculate the obtained average growth rate (R).

6

Then, in a similar growth environment, the growth is controlled by time (t), for a thickness of L, according to:

$$R = R * t$$

(7)

Wherein R is in micron/hour, t is in hour (or converted to seconds), and L is in micron.

Any variations of the teachings above are also meant to be covered and protected by this current application.

The invention claimed is:

1. A semiconductor processing method, said method com-

dipping a semiconductor substrate into a hot liquid comprising elements Si, C, and Al, for a period of time equal

wherein t is equal to (L/R), wherein L is thickness of a grown p-type layer, and R is rate of growth for said grown p-type layer;

wherein L is smaller than thickness of said semiconductor substrate;

pulling out said semiconductor substrate from said hot liquid; and

attaching said grown p-type layer to a piece of radioisotope material.

- 2. The semiconductor processing method as recited in claim 1, wherein one side of said semiconductor substrate is an N-type material.

- 3. The semiconductor processing method as recited in claim 1, wherein one side of said semiconductor substrate is 30 a lightly-doped material.

- 4. The semiconductor processing method as recited in claim 1, wherein said semiconductor substrate is N-type material.

- 5. The semiconductor processing method as recited in 35 claim 1, wherein said semiconductor substrate is a lightlydoped material.

- 6. The semiconductor processing method as recited in claim 1, wherein said semiconductor substrate is from group

- 7. The semiconductor processing method as recited in claim 1, wherein said semiconductor substrate is from group III-V elements.

- **8**. The semiconductor processing method as recited in claim 1, wherein said semiconductor substrate is SiC.

- **9**. The semiconductor processing method as recited in claim 1, wherein temperature of said hot liquid is between 400 degrees C. to 1200 degrees C.

- 10. The semiconductor processing method as recited in claim 1, wherein doping of said semiconductor substrate is smaller than doping of said grown p-type layer.

- 11. The semiconductor processing method as recited in claim 1, wherein said grown p-type layer is highly doped.

- 12. The semiconductor processing method as recited in claim 1, wherein doping of said grown p-type layer is highly

- 13. The semiconductor processing method as recited in claim 1, wherein thickness of said grown p-type layer is 5 nm to 300 nm.

- 14. The semiconductor processing method as recited in claim 1, wherein said grown p-type layer is doped with Al.

- 15. The semiconductor processing method as recited in claim 1, wherein said grown p-type layer is doped at carrier concentrations of between a range of 10<sup>18</sup> cm<sup>-3</sup> to a few times  $10^{20} \, \text{cm}^{-3}$ .

- 16. The semiconductor processing method as recited in claim 1, wherein relative concentration of said elements Si, C, and Al are 94.5%, 0.5% and 5%, respectively.

- 17. The semiconductor processing method as recited in claim 1, wherein relative concentration of said elements Si, C, and Al are less than 95%, 3% and 30%, respectively.

- **18**. The semiconductor processing method as recited in claim **1**, wherein Ge is added with Si, C and Al, with a 5 comprising: concentration of less than 95%.

- 19. The semiconductor processing method as recited in claim 1, wherein said grown p-type layer is on planar SiC.

- 20. The semiconductor processing method as recited in claim 1, wherein said grown p-type layer is on SiC with 10 pillars.

- 21. The semiconductor processing method as recited in claim 1, wherein said semiconductor substrate is integrated with a Si substrate.

- 22. The semiconductor processing method as recited in 15 claim 1, wherein said grown p-type layer is on both sides of said semiconductor substrate.

- 23. The semiconductor processing method as recited in claim 1, wherein said semiconductor substrate has one or more grooves on one or both sides of said semiconductor 20 substrate

8

- **24**. The semiconductor processing method as recited in claim **23**, wherein said one or more grooves are curved, V-shaped, or zig-zag shaped.

- 25. A semiconductor processing method, said method comprising:

- dipping a semiconductor substrate into a hot liquid comprising elements Si, C, and Al, for a period of time equal to t.

- wherein t is equal to (L/R), wherein L is thickness of a grown p-type layer, and R is rate of growth for said grown p-type layer;

- wherein L is smaller than thickness of said semiconductor substrate;

- pulling out said semiconductor substrate from said hot liquid; and

- positioning said grown p-type layer in vicinity of a piece of radioisotope material.

- 26. The semiconductor processing method as recited in claim 25, wherein said radioisotope material is tritium.

\* \* \* \* \*